FPGA内部回路設計開発

概要

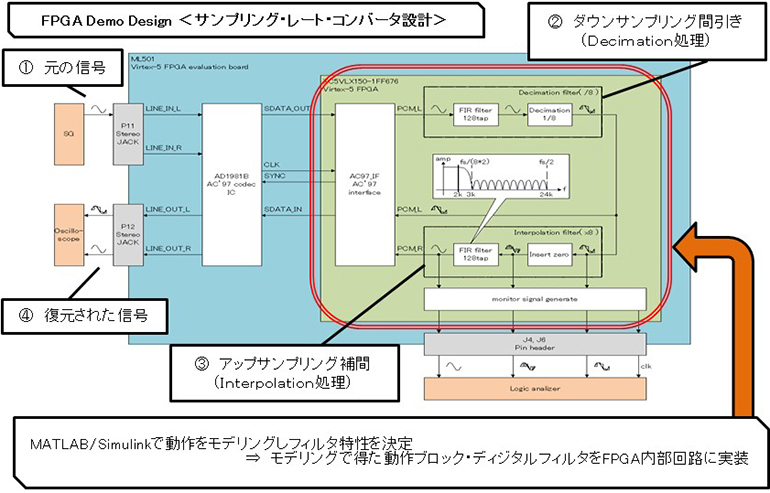

FPGA内部回路設計において、MATLAB/Simulinkでモデリングしアルゴリズムの性能検証をします。

無駄な工数の発生を抑え、「QCD」の向上が図れます。

◆ 回路検討不足による品質低下の軽減

◆ 手戻り作業の抑制による設計コストの圧縮

◆ 手戻り作業の抑制による設計工程の短縮

MATLAB/Simulinkを用いたアルゴリズムのモデリングから、RTL設計、製造、シミュレーションまで

一連のFPGA開発工程をお請けいたします。

VHDL、Verilog-HDLのいずれにも、また、FPGAメーカ各社にも対応いたします。

無駄な工数の発生を抑え、「QCD」の向上が図れます。

◆ 回路検討不足による品質低下の軽減

◆ 手戻り作業の抑制による設計コストの圧縮

◆ 手戻り作業の抑制による設計工程の短縮

MATLAB/Simulinkを用いたアルゴリズムのモデリングから、RTL設計、製造、シミュレーションまで

一連のFPGA開発工程をお請けいたします。

VHDL、Verilog-HDLのいずれにも、また、FPGAメーカ各社にも対応いたします。

写真・図(要点説明)

企業概況

| 企業・団体名 | マリモ電子工業株式会社 | 地域 | その他 |

|---|---|---|---|

| 業種 | ホームページ | http://www.marimo-el.co.jp/ | |

| 企業紹介 | |||

特記事項

| 特許取得・各種認証等取得状況 | 大規模かつ複雑な回路設計が要求される組込システムに応用できます |

|---|